# MICROPROGRAMMED CONTROL • Control Memory

- Sequencing Microinstructions

- Microprogram Example

- Design of Control Unit

- Microinstruction Format

- Nanostorage and Nanoprogram

Microprogrammed Control

#### **COMPARISON OF CONTROL UNIT IMPLEMENTATIONS Control Unit Implementation Combinational Logic Circuits (Hard-wired) Control Data** Memory \_ IR Status F/Fs **Control Unit's State** Timing State Control **Combinational** CPU **Points Logic Circuits** Ins. Cycle State Microprogram Memory **Control Data** Status F/Fs R Control C S C S C P **Next Address Storage** CPU D Generation Ď R (μ-program A R S Logic memorv

Computer Organization

#### **Computer Architectures Lab**

2

Microprogram / Microcode (corresponding to one CPU instruction) - Consists of microinstructions

- Program stored in memory that generates all control signals required to execute the instruction set correctly

Microinstruction

Contains a control word and a sequencing word

Control Word - All control information required for one clock cycle Sequencing Word - Information needed to decide the next microinstruction address

- Control Memory (Control Storage: CS) Storage for microprogram. Generally ROM

## Writeable Control Memory (Writeable Control Storage:WCS)

- CS whose contents can be modified

- -> microprogram

- -> Instruction set

## **Dynamic Microprogramming**

- Computer system whose control unit is implemented with a microprogram in WCS

- Microprogram can be changed by a system programmer or a user

# TERMINOLOGY

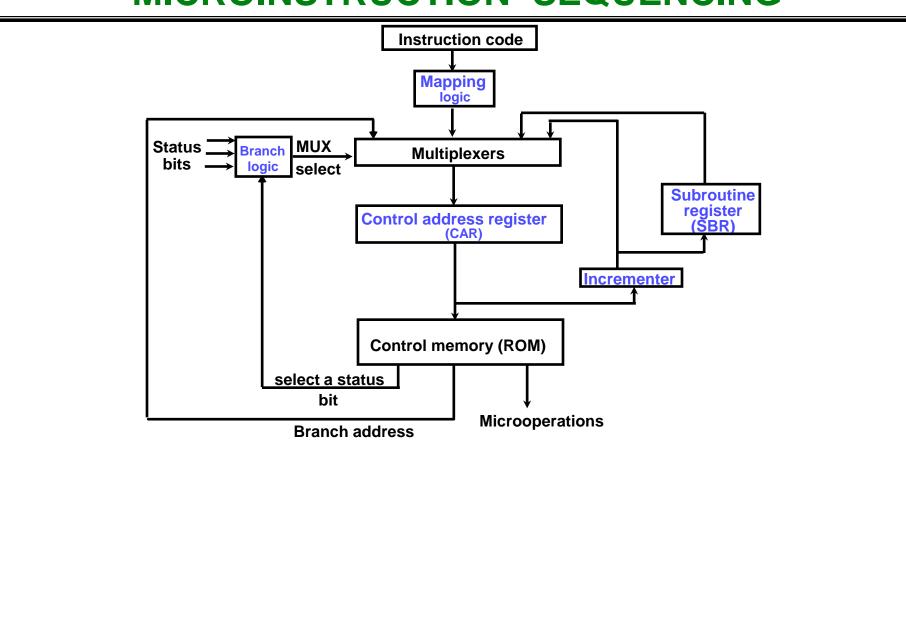

Sequencer (Microprogram Sequencer)

A Microprogram Control Unit that determines the Microinstruction Address to be executed in the next clock cycle

**Sequencing Capabilities Required in a Control Storage**

- Incrementing of the control address register

- Unconditional and conditional branches

- A mapping process from the bits of the machine instruction to an address for control memory

- A facility for subroutine call and return

# **MICROINSTRUCTION SEQUENCING**

**Computer Organization**

# **CONDITIONAL BRANCH**

## **Conditional Branch**

If Condition is true, then Branch (address from the next address field of the current microinstruction) else Fall Through Conditions to Test: O(overflow), N(negative), Z(zero), C(carry), etc.

**Unconditional Branch**

Fixing the value of one status bit at the input of the multiplexer to 1

# **MAPPING OF INSTRUCTIONS**

**Computer Organization**

**Computer Architectures Lab**

7

Microprogrammed Control

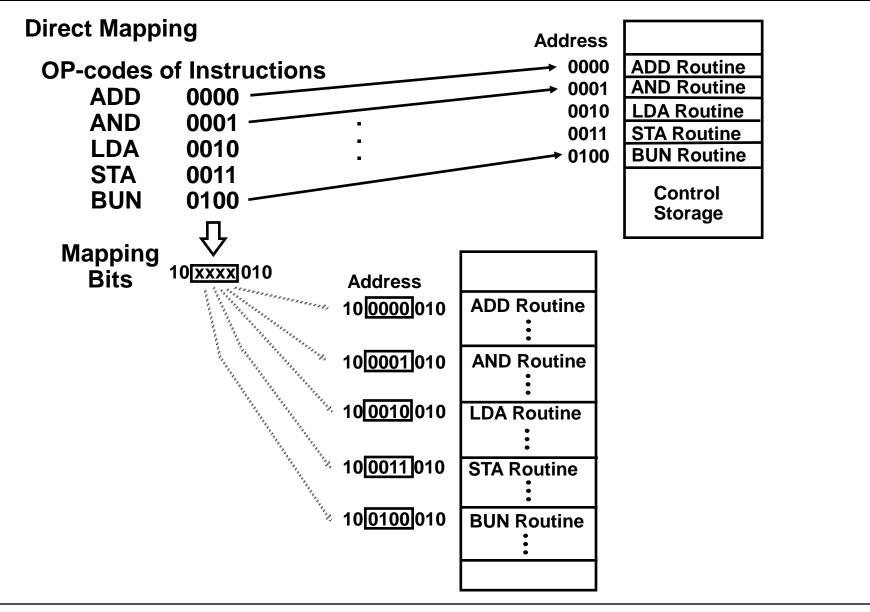

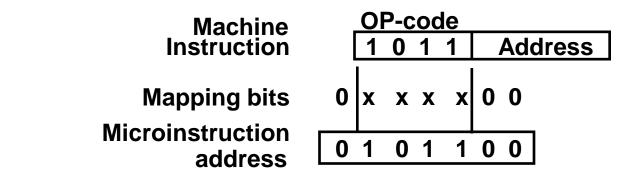

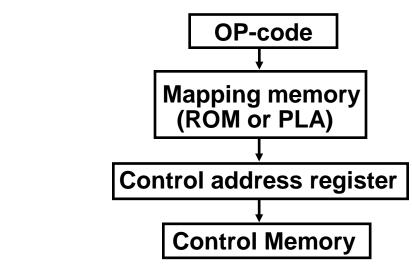

## MAPPING OF INSTRUCTIONS TO MICROROUTINES

Mapping from the OP-code of an instruction to the address of the Microinstruction which is the starting microinstruction of its execution microprogram

Mapping function implemented by ROM or PLA

**Computer Organization**

# MICROPROGRAM EXAMPLE

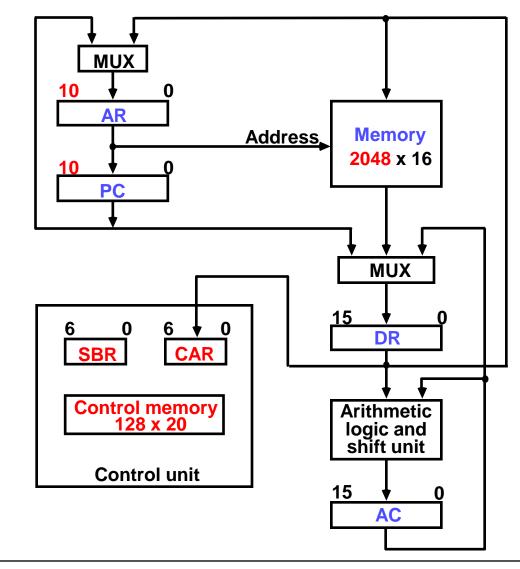

### **Computer Configuration**

**Computer Organization**

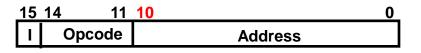

# **MACHINE INSTRUCTION FORMAT**

## **Machine instruction format**

## Sample machine instructions

| Symbol   | OP-code | Description                                |

|----------|---------|--------------------------------------------|

| ADD      | 0000    | $AC \leftarrow AC + M[EA]$                 |

| BRANCH   | 0001    | if (AC < 0) then (PC $\leftarrow$ EA)      |

| STORE    | 0010    | M[EA] ← AC                                 |

| EXCHANGE | 0011    | $AC \leftarrow M[EA], M[EA] \leftarrow AC$ |

EA is the effective address

## **Microinstruction Format**

F1, F2, F3: Microoperation fields CD: Condition for branching BR: Branch field AD: Address field

#### **Computer Organization**

## **MICROINSTRUCTION FIELD DESCRIPTIONS - F1, F2, F3**

| <b>F1</b> | Microoperation          | Symbol |

|-----------|-------------------------|--------|

| 000       | None                    | NOP    |

| 001       | $AC \leftarrow AC + DR$ | ADD    |

| 010       | $AC \leftarrow 0$       | CLRAC  |

| 011       | $AC \leftarrow AC + 1$  | INCAC  |

| 100       |                         | DRTAC  |

| 101       | AR ← DR(0-10)           | DRTAR  |

| 110       | $AR \leftarrow PC$      | PCTAR  |

| 111       | M[AR] ← DR              | WRITE  |

| F2  | Microoperation              | Symbol |

|-----|-----------------------------|--------|

| 000 | None                        | NOP    |

| 001 | $AC \leftarrow AC - DR$     | SUB    |

| 010 | $AC \leftarrow AC \lor DR$  | OR     |

| 011 | $AC \leftarrow AC \land DR$ | AND    |

| 100 | $DR \leftarrow M[AR]$       | READ   |

| 101 | $DR \leftarrow AC$          | ACTDR  |

| 110 | $DR \leftarrow DR + 1$      | INCDR  |

| 111 | DR(0-10) ← PC               | PCTDR  |

| F3  | Microoperation               | Symbol |

|-----|------------------------------|--------|

| 000 | None                         | NOP    |

| 001 | $AC \leftarrow AC \oplus DR$ | XOR    |

| 010 | $AC \leftarrow AC'$          | СОМ    |

| 011 | $AC \leftarrow shI AC$       | SHL    |

| 100 | $AC \leftarrow shr AC$       | SHR    |

| 101 | PC ← PC + 1                  | INCPC  |

| 110 | PC ← AR                      | ARTPC  |

| 111 | Reserved                     |        |

|     |                              |        |

**Computer Organization**

11

## **MICROINSTRUCTION FIELD DESCRIPTIONS - CD, BR**

| CD | Condition  | Symbol | Comments             |

|----|------------|--------|----------------------|

| 00 | Always = 1 | U      | Unconditional branch |

| 01 | DR(15)     | 1      | Indirect address bit |

| 10 | AC(15)     | S      | Sign bit of AC       |

| 11 | AC = 0     | Z      | Zero value in AC     |

| BR | Symbol | Function                                                        |

|----|--------|-----------------------------------------------------------------|

| 00 | JMP    | $CAR \leftarrow AD$ if condition = 1                            |

|    |        | $CAR \leftarrow CAR + 1$ if condition = 0                       |

| 01 | CALL   | $CAR \leftarrow AD$ , $SBR \leftarrow CAR + 1$ if condition = 1 |

|    |        | $CAR \leftarrow CAR + 1$ if condition = 0                       |

| 10 | RET    | CAR ← SBR (Return from subroutine)                              |

| 11 | MAP    | CAR(2-5) ← DR(11-14), CAR(0,1,6) ← 0                            |

Microprogrammed Control

# SYMBOLIC MICROINSTRUCTIONS

- Symbols are used in microinstructions as in assembly language

- A symbolic microprogram can be translated into its binary equivalent by a microprogram assembler.

| Sample Form<br>five fiel |                                             | D; BR; AD                                                                                  |

|--------------------------|---------------------------------------------|--------------------------------------------------------------------------------------------|

| Label:                   |                                             | ay specify a symbolic<br>ninated with a <mark>colon</mark>                                 |

| Micro-o                  | ps: consists of one, two, or<br>separated b | •                                                                                          |

| CD:                      | one of { <mark>U, I, S, Z</mark> }, where   | U: Unconditional Branch<br>I: Indirect address bit<br>S: Sign of AC<br>Z: Zero value in AC |

| BR:                      | one of {JMP, CALL, RET, N                   | IAP}                                                                                       |

| AD:                      | one of {Symbolic address                    | , NEXT, empty}                                                                             |

**Computer Organization**

# **SYMBOLIC MICROPROGRAM - FETCH ROUTINE**

During FETCH, Read an instruction from memory and decode the instruction and update PC

Sequence of microoperations in the fetch cycle:

$\begin{array}{l} \mathsf{AR} \leftarrow \mathsf{PC} \\ \mathsf{DR} \leftarrow \mathsf{M}[\mathsf{AR}], \mathsf{PC} \leftarrow \mathsf{PC} + 1 \\ \mathsf{AR} \leftarrow \mathsf{DR}(0\text{-}10), \mathsf{CAR}(2\text{-}5) \leftarrow \mathsf{DR}(11\text{-}14), \mathsf{CAR}(0,1,6) \leftarrow 0 \end{array}$

Symbolic microprogram for the fetch cycle:

|        | ORG <mark>64</mark> |   |     |      |

|--------|---------------------|---|-----|------|

| FETCH: | PCTAR               | U | JMP | NEXT |

|        | READ, INCPC         | U | JMP | NEXT |

|        | DRTAR               | U | MAP |      |

Binary equivalents translated by an assembler

| Binary<br>address | F1  | F2  | F3  | CD | BR | AD      |

|-------------------|-----|-----|-----|----|----|---------|

| 100000            | 110 | 000 | 000 | 00 | 00 | 1000001 |

| 1000001           | 000 | 100 | 101 | 00 | 00 | 1000010 |

| 1000010           | 101 | 000 | 000 | 00 | 11 | 000000  |

**Computer Organization**

## SYMBOLIC MICROPROGRAM

- Control Storage: 128 20-bit words

- The first 64 words: Routines for the 16 machine instructions (as 4 bits in op code field)

- The last 64 words: Used for other purpose (e.g., fetch routine and other subroutines)

- Mapping: OP-code XXXX into 0XXXX00, the first address for the 16 routines are 0(0 0000 00), 4(0 0001 00), 8, 12, 16, 20, ..., 60

#### **Partial Symbolic Microprogram**

|           |              | <u>I</u> - J |      |        |

|-----------|--------------|--------------|------|--------|

| Label     | Microops     | CD           | BR   | AD     |

|           | ORG 0        | _            |      |        |

| ADD:      | NOP          | I            | CALL | INDRCT |

|           | READ         | U            | JMP  | NEXT   |

|           | ADD          | U            | JMP  | FETCH  |

|           | ORG 4        |              |      |        |

| BRANCH:   | NOP          | S            | JMP  | OVER   |

|           | NOP          | Ū            | JMP  | FETCH  |

| OVER:     | NOP          | Ī            | CALL | INDRCT |

|           | ARTPC        | U            | JMP  | FETCH  |

|           |              |              |      |        |

|           | ORG 8        | _            |      |        |

| STORE:    | NOP          | I            | CALL | INDRCT |

|           | ACTDR        | U            | JMP  | NEXT   |

|           | WRITE        | U            | JMP  | FETCH  |

|           | ORG 12       |              |      |        |

| EXCHANGE: | NOP          | 1            | CALL | INDRCT |

|           | READ         | Ū            | JMP  | NEXT   |

|           | ACTDR, DRTAC | Ŭ            | JMP  | NEXT   |

|           | WRITE        | Ŭ            | JMP  | FETCH  |

|           | ORG 64       |              |      |        |

| FETCH:    | PCTAR        | U            | JMP  | NEXT   |

|           | READ, INCPC  | Ŭ            | JMP  | NEXT   |

|           | DRTAR        | Ŭ            | MAP  |        |

| INDRCT:   | READ         | Ŭ            | JMP  | NEXT   |

|           | DRTAR        | ŭ            | RET  |        |

|           |              |              |      |        |

|           |              |              |      |        |

**INDRCT:**

when I=1, say, for ADD at 0 address, and to get Effective Address of data a branch to INDRCT (a subroutine) occurs and SBR  $\leftarrow$  return address (1 in this case).

**RET** from subroutine INDRCT CAR← SBR

**Computer Organization**

## **BINARY MICROPROGRAM**

|               | Addr    | ess     |     | Binary | Microinstr | uction |    |         |

|---------------|---------|---------|-----|--------|------------|--------|----|---------|

| Micro Routine | Decimal | Binary  | F1  | F2     | F3         | CD     | BR | AD      |

| ADD           | 0       | 000000  | 000 | 000    | 000        | 01     | 01 | 1000011 |

|               | 1       | 0000001 | 000 | 100    | 000        | 00     | 00 | 0000010 |

|               | 2       | 0000010 | 001 | 000    | 000        | 00     | 00 | 1000000 |

|               | 3       | 0000011 | 000 | 000    | 000        | 00     | 00 | 1000000 |

| BRANCH        | 4       | 0000100 | 000 | 000    | 000        | 10     | 00 | 0000110 |

|               | 5       | 0000101 | 000 | 000    | 000        | 00     | 00 | 1000000 |

|               | 6       | 0000110 | 000 | 000    | 000        | 01     | 01 | 1000011 |

|               | 7       | 0000111 | 000 | 000    | 110        | 00     | 00 | 1000000 |

| STORE         | 8       | 0001000 | 000 | 000    | 000        | 01     | 01 | 1000011 |

|               | 9       | 0001001 | 000 | 101    | 000        | 00     | 00 | 0001010 |

|               | 10      | 0001010 | 111 | 000    | 000        | 00     | 00 | 1000000 |

|               | 11      | 0001011 | 000 | 000    | 000        | 00     | 00 | 1000000 |

| EXCHANGE      | 12      | 0001100 | 000 | 000    | 000        | 01     | 01 | 1000011 |

|               | 13      | 0001101 | 001 | 000    | 000        | 00     | 00 | 0001110 |

|               | 14      | 0001110 | 100 | 101    | 000        | 00     | 00 | 0001111 |

|               | 15      | 0001111 | 111 | 000    | 000        | 00     | 00 | 1000000 |

| FETCH         | 64      | 1000000 | 110 | 000    | 000        | 00     | 00 | 1000001 |

|               | 65      | 1000001 | 000 | 100    | 101        | 00     | 00 | 1000010 |

|               | 66      | 1000010 | 101 | 000    | 000        | 00     | 11 | 0000000 |

| INDRCT        | 67      | 1000011 | 000 | 100    | 000        | 00     | 00 | 1000100 |

|               | 68      | 1000100 | 101 | 000    | 000        | 00     | 10 | 0000000 |

#### This microprogram can be implemented using ROM

| Computer Organization | Comp | uter | Organ | nization |

|-----------------------|------|------|-------|----------|

|-----------------------|------|------|-------|----------|

Computer Architectures Lab

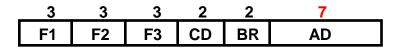

#### DESIGN OF CONTROL UNIT - DECODING MICROOPERATIONAL FIELDS-

17

Few functions are shown as outputs of 3 decoders Note:

Instead of using gates to generate control signals for ADD, AND, and DRTAC these will become now outputs of MUX

**Computer Organization**

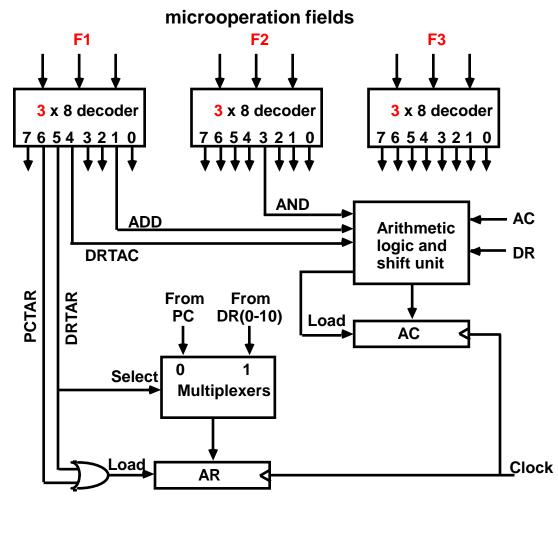

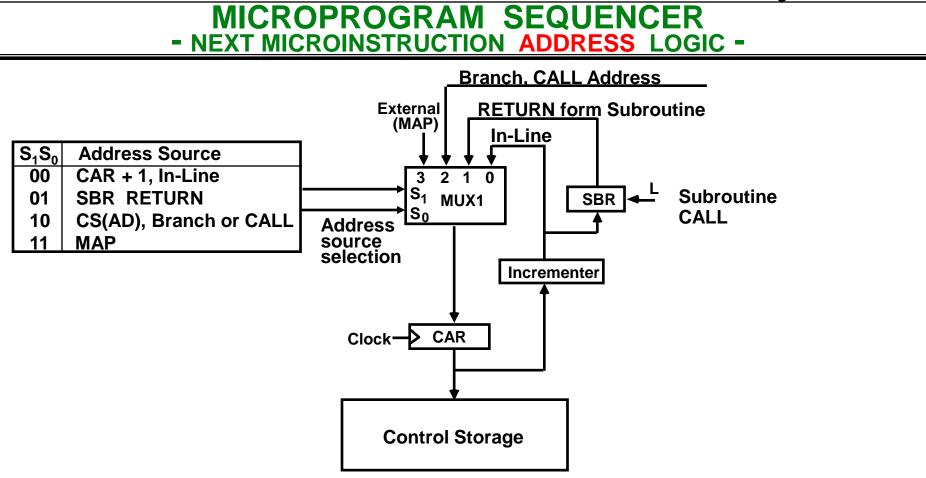

MUX-1 selects an address from one of four sources and routes it into a CAR

- In-Line Sequencing  $\rightarrow$  CAR + 1

- Branch, Subroutine Call  $\rightarrow$  CS(AD)

- Return from Subroutine  $\rightarrow$  Output of SBR

- New Machine instruction  $\rightarrow$  MAP

**Computer Organization**

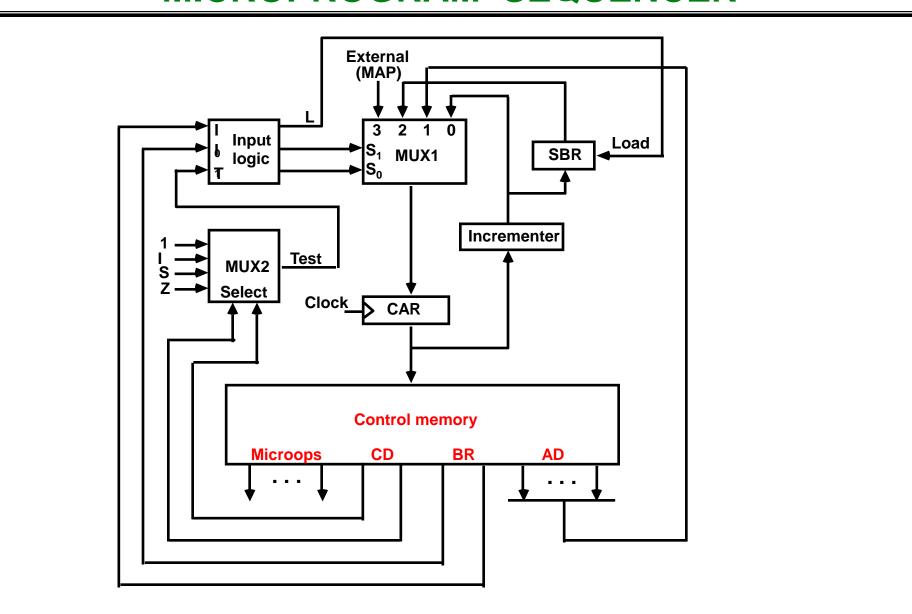

#### 19 MICROPROGRAM SEQUENCER - CONDITION AND BRANCH CONTROL -L(load SBR with PC) L From Test MUX2 for subroutine Call CPU Input BR field Select logic S₀ for next address of CS S₁ selection 1 **CD** Field of CS **Input Logic** Meaning Source of Address $S_1S_0$ L I₀I₁T 000 In-Line CAR+1 00 0 001 JMP CS(AD) 10 0 010 In-Line CAR+1 0 00 1 011 CALL CS(AD) and SBR <- CAR+1 10 RET 10x SBR 01 0

11

0

$$S_0 = I_0$$

$S_1 = I_0 I_1 + I_0'T$

$L = I_0' I_1 T$

DR(11-14)

**Computer Organization**

11x

MAP

## **MICROPROGRAM SEQUENCER**

**Computer Organization**